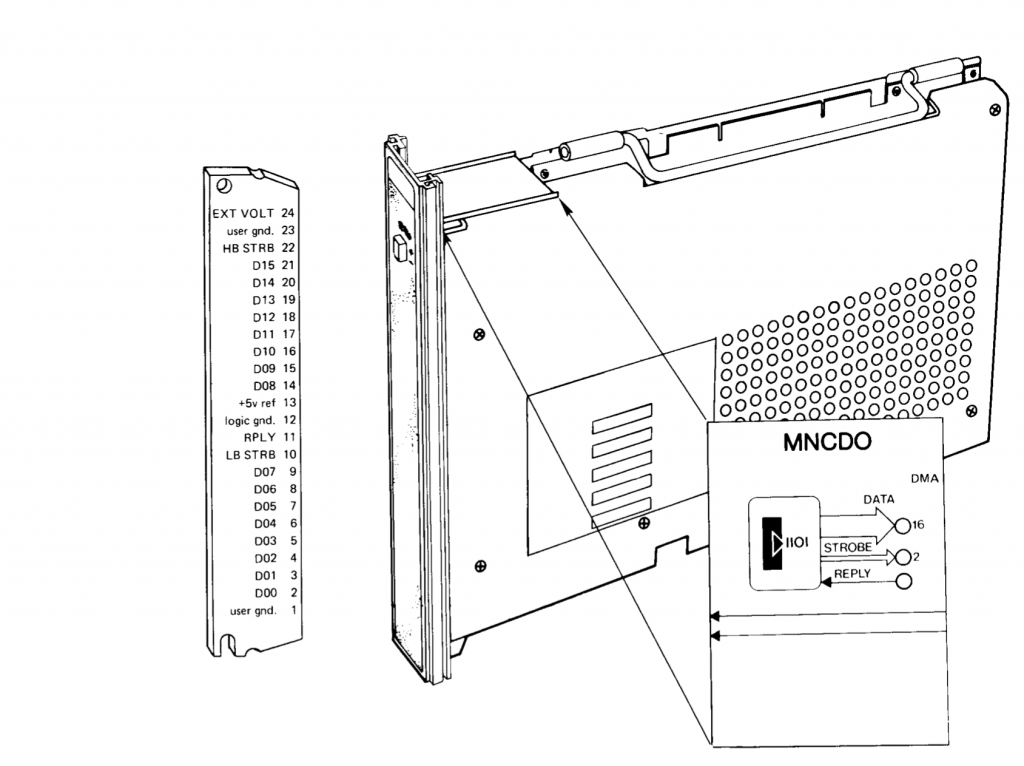

The MNCDO is a digital output module for 16 digital lines. The lines can be used individually, or in two groups of 8, or in one group of 16. For the last two variants, there are two strobe signals to signal update events.

MNCDO0 CSR 171260 VEC 340 BR 4 MNCDO1 CSR 171264 VEC 344 BR 4 MNCDO2 CSR 171270 VEC 350 BR 4 MNCDO3 CSR 171274 VEC 354 BR 4

MNCDO has two registers: a CSR @ 171260, and the DOR Data Output Register @ 171262. The CSR is relatively simple, compared to most MINC modules – there are only a few control bits, and the MNCDO only uses one interrupt vector.

A system can have between 0 and 4 MNCDO. The VMNE test mentions support for 8 modules, but MINC BASIC will not work with more than 4. Modules should use consecutive addresses starting with the CSR and vector as mentioned above.

MNCDO CSR

| 8 | maint (w/o) reads as 0 when written ‘1’, simulates a pulse on the reply input. Possibly this should only work when a byte access is done. |

| 7 | done (r/w) the done bit will be set when the external reply signal is pulsed. It is cleared by writing to the DOR register, or by direct writing to the CSR. When set, if the ie bit is set, an interrupt will be triggered. |

| 6 | ie (r/w) interrupt enable; when set, an interrupt will be triggered when the done bit is set. |

| 4 | defeat panel sw (r/w) presumably, this bit disables the front panel signal invert switch. |

| 3 | pos edge reply (r/w) presumably, this bit reverses the polarity of the reply input. |

Information sources

The information in this page is mainly based on the VMNE test output and the schematic.

Unknown/Missing information

There might be more CSR bits than I’ve found so far; and the bits 4 and 3 are just based on the schematic – ie, not verified by test software etc.

Implementation status

The current implementation passes the VMNE test without error, and can be used with MINC BASIC. The CSR bits 4 and 3 are not currently implemented.

MINC BASIC considerations

The only statement that interacts with the module directly is DOUT. The DOUT_MASK appears to be software-only.

The module is used in two distinct ways: either the data is simply written to the DOR (Data Output Register); or, alternatively, the CSR is set up for interrupting. This latter method is only used when DOUT is called with a data_length of >1; this causes the statement to wait until the reply signal is pulsed before the next value is output; and the statement will only finish after data_length pulses have been received.

MINC BASIC does not use the high and low strobes distinctly; both always pulse together. This is mentioned in the MINC documentation.